# **AFIPS**

CONFERENCE PROCEEDINGS

**VOLUME 40**

1972

SPRING JOINT COMPUTER CONFERENCE

May 16-18, 1972 Atlantic City, New Jersey

AFIPS PRESS

210 SUMMIT AVENUE MONTVALE, NEW JERSEY 07645 The ideas and opinions expressed herein are solely those of the authors and are not necessarily representative of or endorsed by the 1972 Spring Joint Computer Conference Committee or the American Federation of Information Processing Societies, Inc.

Library of Congress Catalog Card Number 55-44701

AFIPS PRESS

210 Summit Avenue

Montvale, New Jersey 07645

©1972 by the American Federation of Information Processing Societies, Inc., Montvale, New Jersey 07645. All rights reserved. This book, or parts thereof, may not be reproduced in any form without permission of the publisher.

### **CONTENTS**

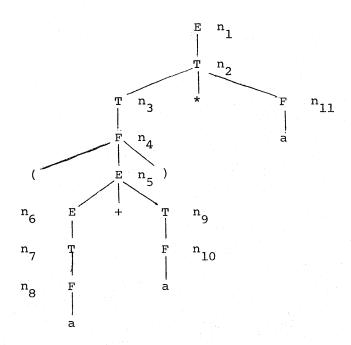

| IMPLEMENTATION OF PROGRAMMING LANGUAGE PROCESSORS                                                                             |            |                                                     |

|-------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------|

| An appraisal of compiler technology                                                                                           | 1<br>11    | R. M. McClure<br>T. E. Cheatham, Jr.<br>B. Wegbreit |

| Segmentation and optimization of programs from cyclic structure analysis                                                      | 23         | J. Baer                                             |

| FRONTIERS OF LARGE-SCALE SCIENTIFIC COMPUTATION                                                                               |            | R. Caughey                                          |

| The interplay of computer science and large-scale scientific calculation.                                                     | 37         | K. K. Curtis                                        |

| Computer architecture and very large problems                                                                                 | 45<br>51   | R. B. Lazarus<br>M. S. Lynn                         |

| THE COMPUTER AS SUPERTOY—PANEL SESSION                                                                                        |            |                                                     |

| (No papers in this volume)                                                                                                    |            |                                                     |

| TRAINING COMMERCIAL PROGRAMMERS AND SYSTEMS ANALYSTS                                                                          |            |                                                     |

| The functions and elements of a training system                                                                               | 53         | B. Jones                                            |

| Planning data processing education to meet job requirements                                                                   | 59         | J. O. Hammond                                       |

| Modular training—A new emphasis                                                                                               | 69<br>77   | R. W. Kleffman<br>G. A. Smith                       |

| SOFTWARE DESIGN FOR THE MINI-COMPUTER                                                                                         |            |                                                     |

| The future of mini-computer programming                                                                                       | 103        | D. Waks<br>A. B. Kronenberg                         |

| The current state of mini-computer software                                                                                   | 111<br>119 | J. Ossanna<br>J. R. Allen<br>S. S. Yau              |

| TECHNIQUES FOR DEVELOPING LARGE PROGRAMMING SYSTEMS                                                                           |            | s. s. Tau                                           |

| An organization for successful project management                                                                             | 129        | D. Smith                                            |

| Commercial data processing machines in government applications                                                                | 141        | J. D. Aron                                          |

| Programming language efficiency in real-time software systems                                                                 | 155        | R. E. Merwin<br>J. O. Henriksen                     |

| MATHEMATICAL OPTIMIZATION THEORY AND ALGORITHMS                                                                               |            |                                                     |

| A review of recursive filtering algorithms                                                                                    | 163        | B. Friedland                                        |

| On computational methods for dynamic and static optimization                                                                  | 181        | D. H. Jacobsen                                      |

| Piecewise linear approximations of fewest line segments<br>Experimental results on a new computer method for generating opti- | 187        | D. G. Wilson                                        |

| mal policy variables in (s,S) inventory control problem                                                                       | 199        | P. E. Valisalo                                      |

|                                                                                                                               |            | B. D. Sivazlian<br>J. F. Maillot                    |

| NEW THEORETICAL FRONTIERS OF COMPUTER SCIENCE                                                                                 |            |                                                     |

| Bounds on multiprocessing anomalies and packing algorithms                                                                    | 205        | R. L. Graham                                        |

| Computation of recursive programs—Theory vs practice                                                                          | 219        | Z. Manna                                            |

| Mathematical concepts in programming language semantics                                                                       | 225        | D. Scott                                            |

| Applications of language theory to compiler design                                                                            | 235        | J. D. Ullman                                        |

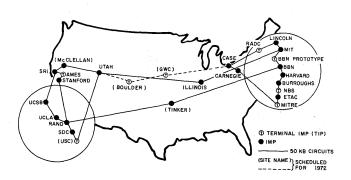

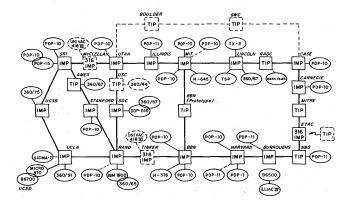

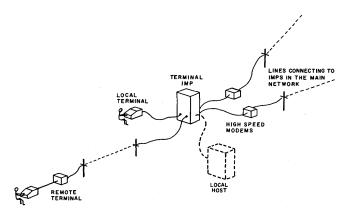

| The terminal IMP for the ARPA computer network.  243 S. M. Ornstein F. E. Heart W. R. Crowther H. K. Rising S. B. Russell A. Michel  Computer communication network design—Experience with theory and practice.  Computer communication network design—Experience with theory and practice.  Experience with theory and practice.  Function-oriented protocols for the ARPA computer network.  Extension of protocols for the ARPA computer network.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  Extensio | THE ARPA NETWORK                                                         |     |                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-------------------------|

| E. E. Heart W. R. Crowther H. K. Rising S. B. Russell A. Michel  Computer communication network design—Experience with theory and practice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | The terminal IMP for the ARPA computer network                           | 243 | S. M. Ornstein          |

| Computer communication network design—Experience with theory and practice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | The terminal that for the first it computed network                      | 210 |                         |

| Computer communication network design—Experience with theory and practice.  Computer communication network design—Experience with theory and practice.  Experience with theory and pract |                                                                          |     | W. R. Crowther          |

| Computer communication network design—Experience with theory and practice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                          |     | H. K. Rising            |

| Computer communication network design—Experience with theory and practice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                          |     |                         |

| and practice. 255 H. Frank R. E. Kahn L. Kleinrock Function-oriented protocols for the ARPA computer network 271 S. D. Crocker J. Heafner J. Metcalfe J. Postel McROSS—A multi-computer programming system 281 R. H. Thomas D. A. Henderson, Extension of packet communication technology to a hand-held personal terminal 295 L. G. Roberts  PROGRAMMING LANGUAGES FOR SPECIALIZED APPLICATION AREAS An overview of programming languages for special application areas 299 J. E. Sammet The future of specialized languages 313 F. B. Thompson B. H. Dostert AMBUSH—A case history in language design 321 S. Warshall The data-text system—An application language for the social sciences 333 D. J. Armor  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS LSI—Implications for future design and architecture 343 S. F. Dennis M. G. Smith The rationale for logic from semiconductor memory 353 W. H. Davidow SYMBOL hardware debugging facilities 359 M. A. Calhoun The Rice Research Computer—A tagged architecture 369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS A generative CAI tutor for computer science concepts 379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine 391 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                          |     | A. Michel               |

| Function-oriented protocols for the ARPA computer network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                          |     | TT 73 1                 |

| Function-oriented protocols for the ARPA computer network                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | and practice                                                             | 255 |                         |

| Function-oriented protocols for the ARPA computer network 271 S. D. Crocker J. Heafner J. Metcalfe J. Postel  McROSS—A multi-computer programming system 281 R. H. Thomas D. A. Henderson,  Extension of packet communication technology to a hand-held personal terminal 295 L. G. Roberts  PROGRAMMING LANGUAGES FOR SPECIALIZED APPLICATION AREAS  An overview of programming languages for special application areas 299 J. E. Sammet The future of specialized languages 313 F. B. Thompson B. H. Dostert AMBUSH—A case history in language design 321 S. Warshall The data-text system—An application language for the social sciences 333 D. J. Armor  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture 343 S. F. Dennis M. G. Smith The rationale for logic from semiconductor memory 353 W. H. Davidow SYMBOL hardware debugging facilities 359 M. A. Calhoun The Rice Research Computer—A tagged architecture 369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts 379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine 391 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                          |     |                         |

| McROSS—A multi-computer programming system. 281 R. H. Thomas Extension of packet communication technology to a hand-held personal terminal. 295 L. G. Roberts  PROGRAMMING LANGUAGES FOR SPECIALIZED APPLICATION AREAS  An overview of programming languages for special application areas. 299 J. E. Sammet The future of specialized languages. 313 F. B. Thompson B. H. Dostert AMBUSH—A case history in language design. 321 S. Warshall The data-text system—An application language for the social sciences. 333 D. J. Armor  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture. 343 S. F. Dennis M. G. Smith The rationale for logic from semiconductor memory. 353 W. H. Davidow SYMBOL hardware debugging facilities. 359 M. A. Calhoun The Rice Research Computer—A tagged architecture. 369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS A generative CAI tutor for computer science concepts. 379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine. 391 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Function eviented protectle for the ADDA computer network                | 971 |                         |

| McROSS—A multi-computer programming system.  McROSS—A multi-computer programming system.  Extension of packet communication technology to a hand-held personal terminal.  Extension of packet communication technology to a hand-held personal terminal.  PROGRAMMING LANGUAGES FOR SPECIALIZED APPLICATION AREAS  An overview of programming languages for special application areas.  An overview of programming languages.  B. H. Dostert  S. Warshall  The data-text system—An application language for the social sciences.  321 S. Warshall  The data-text system—An application language for the social sciences.  333 D. J. Armor  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture.  343 S. F. Dennis M. G. Smith  The rationale for logic from semiconductor memory.  353 W. H. Davidow SYMBOL hardware debugging facilities.  359 M. A. Calhoun The Rice Research Computer—A tagged architecture.  369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts.  379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine.  381 J. K. Clema R. L. Didday M. Wesseler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | runction-oriented protocols for the ARPA computer network                | 2/1 |                         |

| McROSS—A multi-computer programming system.  Extension of packet communication technology to a hand-held personal terminal.  PROGRAMMING LANGUAGES FOR SPECIALIZED APPLICATION AREAS  An overview of programming languages for special application areas.  An overview of programming languages for special application areas.  Ambush—A case history in language design.  The data-text system—An application language for the social sciences.  321 S. Warshall  The data-text system—An application language for the social sciences.  333 D. J. Armor  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture.  343 S. F. Dennis M. G. Smith  The rationale for logic from semiconductor memory.  353 W. H. Davidow SYMBOL hardware debugging facilities.  359 M. A. Calhoun The Rice Research Computer—A tagged architecture.  369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts.  379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine.  311 R. H. Thomas D. A. Henderson, D. A. G. Roberts  409 J. E. Sammet D. A. G. Roberts  410 J. E. Koffman D. J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                  |                                                                          |     |                         |

| McROSS—A multi-computer programming system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                          |     |                         |

| Extension of packet communication technology to a hand-held personal terminal.  PROGRAMMING LANGUAGES FOR SPECIALIZED APPLICATION AREAS  An overview of programming languages for special application areas. The future of specialized languages.  An Overview of programming languages for special application areas. The future of specialized languages.  AMBUSH—A case history in language design.  The data-text system—An application language for the social sciences.  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture.  SYMBOL hardware debugging facilities.  The rationale for logic from semiconductor memory.  SYMBOL hardware debugging facilities.  The Rice Research Computer—A tagged architecture.  A generative CAI tutor for computer science concepts.  A generative CAI tutor for computer science concepts.  Preliminary thoughts about a UNIversal TEAching Machine.  J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | McROSS—A multi-computer programming system                               | 281 |                         |

| Extension of packet communication technology to a hand-held personal terminal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 11 mail compact programming system (111111111111111111111111111111111111 |     |                         |

| PROGRAMMING LANGUAGES FOR SPECIALIZED APPLICATION AREAS  An overview of programming languages for special application areas                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Extension of packet communication technology to a hand-held per-         |     | 2. 11. 110114018011, 01 |

| APPLICATION AREAS  An overview of programming languages for special application areas. 299 J. E. Sammet The future of specialized languages 313 F. B. Thompson B. H. Dostert AMBUSH—A case history in language design 321 S. Warshall The data-text system—An application language for the social sciences 333 D. J. Armor  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture 343 S. F. Dennis M. G. Smith The rationale for logic from semiconductor memory 353 W. H. Davidow SYMBOL hardware debugging facilities 359 M. A. Calhoun The Rice Research Computer—A tagged architecture 369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts 379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine 391 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | - · · · · · · · · · · · · · · · · · · ·                                  | 295 | L. G. Roberts           |

| APPLICATION AREAS  An overview of programming languages for special application areas. 299 J. E. Sammet The future of specialized languages. 313 F. B. Thompson B. H. Dostert AMBUSH—A case history in language design. 321 S. Warshall The data-text system—An application language for the social sciences. 333 D. J. Armor  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture. 343 S. F. Dennis M. G. Smith The rationale for logic from semiconductor memory. 353 W. H. Davidow SYMBOL hardware debugging facilities. 359 M. A. Calhoun The Rice Research Computer—A tagged architecture. 369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts. 379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine. 391 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | PROCE ANALYSIS LANGUAGES FOR SPECIALIZED                                 |     |                         |

| An overview of programming languages for special application areas.  The future of specialized languages.  The future of specialized languages.  AMBUSH—A case history in language design.  The data-text system—An application language for the social sciences.  The data-text system—An application language for the social sciences.  The ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture.  SYSTEMS  LSI—Implications for future design and architecture.  The rationale for logic from semiconductor memory.  SYMBOL hardware debugging facilities.  SYMBOL hardware debugging facilities.  The Rice Research Computer—A tagged architecture.  The Rice Research Computer—A tagged architecture.  A generative CAI tutor for computer science concepts.  A generative CAI tutor for computer science concepts.  Preliminary thoughts about a UNIversal TEAching Machine.  313 F. B. Thompson B. H. Dostert S. Warshall  S. Warshall  D. J. Armor  324 S. F. Dennis M. G. Smith  M. G. Smith  W. H. Davidow  SYMBOL hardware debugging facilities.  359 M. A. Calhoun  The Rice Research Computer—A tagged architecture.  369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts.                                                                                                                                                 |                                                                          |     |                         |

| The future of specialized languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | APPLICATION AREAS                                                        |     |                         |

| AMBUSH—A case history in language design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | An overview of programming languages for special application areas       | 299 | J. E. Sammet            |

| AMBUSH—A case history in language design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | The future of specialized languages                                      | 313 | F. B. Thompson          |

| The data-text system—An application language for the social sciences.  NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture.  LSI—Implications for future design and architecture.  SYMBOL hardware debugging facilities.  The Rice Research Computer—A tagged architecture.  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts.  A generative CAI tutor for computer science concepts.  Preliminary thoughts about a UNIversal TEAching Machine.  333 D. J. Armor  333 D. J. Armor  343 S. F. Dennis M. G. Smith M. G. Smith M. A. Calhoun SYMBOL hardware debugging facilities.  359 M. A. Calhoun 369 E. A. Feustel  369 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine.  379 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |     | B. H. Dostert           |

| NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          | 321 | S. Warshall             |

| NEW TRENDS IN THE ARCHITECTURE OF COMPUTER SYSTEMS  LSI—Implications for future design and architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                          | 333 | D. J. Armor             |

| LSI—Implications for future design and architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Sciences                                                                 | 000 | D. U. IIIIIOI           |

| LSI—Implications for future design and architecture.  343 S. F. Dennis M. G. Smith The rationale for logic from semiconductor memory.  353 W. H. Davidow SYMBOL hardware debugging facilities.  359 M. A. Calhoun The Rice Research Computer—A tagged architecture.  369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts.  379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine.  391 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                          |     |                         |

| M. G. Smith The rationale for logic from semiconductor memory. 353 W. H. Davidow SYMBOL hardware debugging facilities. 359 M. A. Calhoun The Rice Research Computer—A tagged architecture. 369 E. A. Feustel  COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts. 379 E. Koffman Preliminary thoughts about a UNIversal TEAching Machine. 391 J. K. Clema R. L. Didday M. Wessler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SYSTEMS                                                                  |     |                         |

| The rationale for logic from semiconductor memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LSI—Implications for future design and architecture                      | 343 | S. F. Dennis            |

| SYMBOL hardware debugging facilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                          |     | M. G. Smith             |

| The Rice Research Computer—A tagged architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The rationale for logic from semiconductor memory                        | 353 | W. H. Davidow           |

| COMPUTERS IN INSTRUCTION—SOME CONSIDERATIONS  A generative CAI tutor for computer science concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                          | 359 |                         |

| A generative CAI tutor for computer science concepts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | The Rice Research Computer—A tagged architecture                         | 369 | E. A. Feustel           |